👏 Paper title: Graph Neural Networks Automated Design and Deployment on Device-Edge Co-Inference Systems. In this paper, we abstract the communication process in device-edge co-inference into a specific operation, creating a unified design space for GNN architecture and co-inference schemes. Using random search, we achieve joint optimization, leading to a GNN architecture that integrates partitioning schemes, enabling a trade-off between communication and computation, and outperforming SOTA methods. [related project]

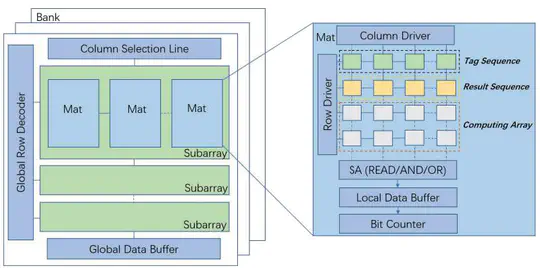

👏 Paper title: Towards Efficient SRAM-PIM Architecture Design by Exploiting Unstructured Bit-Level Sparsity. In this paper, we propose Dyadic Block PIM (DB-PIM), a groundbreaking algorithm-architecture co-design framework to exploit the unstructured bit-level sparsity effectively. First, we propose an algorithm coupled with a distinctive sparsity pattern to preserve the random distribution of non-zero bits while improving regularity. Then, we develop a custom PIM macro that includes dyadic block multiplication units (DBMUs) and Canonical Signed Digit (CSD)-based adder trees to achieve unstructured bit-level sparsity. Results show that our proposed co-design framework achieves a remarkable speedup of up to 6.53x and energy savings of 77.50%. [related project]

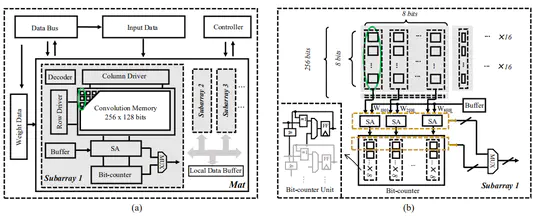

👏 Paper title: DDC-PIM: Efficient Algorithm/Architecture Co-Design for Doubling Data Capacity of SRAM-Based Processing-in-Memory. We propose DDC-PIM, an efficient algorithm/architecture co-design methodology that effectively doubles the equivalent data capacity of SRAM. By combining qvfilter-wise complementary correlation algorithm with a customized architecture, we can exploit the intrinsic cross-coupled structure of 6T SRAM to store the bitwise complementary pair in their complementary states (Q/QB), thereby maximizing the data capacity and integration density of each SRAM cell. [related project]

👏 Paper title: Architectural Implications of GNN Aggregation Programming Abstractions. This paper evaluates the architectural implications of programming abstractions for Graph Neural Network (GNN) aggregation. It introduces a taxonomy based on data organization and propagation methods and performs a comprehensive performance characterization across platforms and graph properties. Key findings include insights into abstraction selection, hardware adaptability, and the structural impact of graphs, providing valuable guidance for GNN acceleration research. [related project]

👏 Paper title: Lossy and Lossless (L2) Post-training Model Size Compression. We propose a unified post-training model size compression method that combines lossy and lossless compression techniques, with a parametric weight transformation and a differentiable counter to guide optimization. Our method achieves a stable 10× compression ratio without accuracy loss and a 20× ratio with minimal accuracy degradation, all while easily controlling the global compression ratio and adapting it for different layers. [related project]

👏 Paper title: Hardware-Aware Graph Neural Network Automated Design for Edge Computing Platforms. We explore a hardware-aware GNN architecture design for edge devices, leveraging the novel idea of “predicting GNNs with GNNs” to efficiently estimate the performance of candidate architectures during the NAS process. By thoroughly analyzing the impact of device heterogeneity on GNN performance and integrating hardware awareness into the exploration, our method achieves significant improvements in both accuracy and efficiency. [related project]

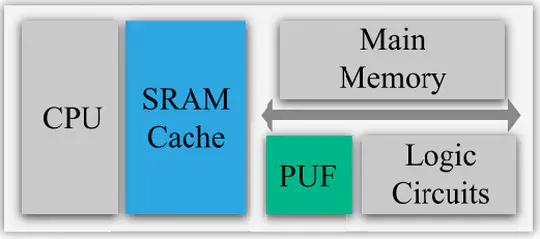

👏 Paper title: Reconfigurable and Dynamically Transformable In-Cache-MPUF System With True Randomness Based on the SOT-MRAM. In this paper, we present a reconfigurable Physically Unclonable Functions (PUF) based on the Spin-Orbit-Torque Magnetic Random-Access Memory (SOT-MRAM), which exploits thermal noise as the true dynamic entropy source. [related project]

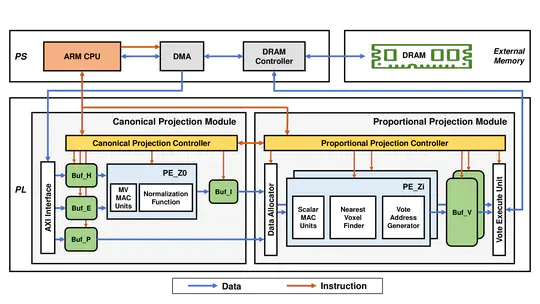

👏 Paper title: Eventor: An Efficient Event-Based Monocular Multi-View Stereo Accelerator on FPGA Platform. In this paper, Eventor is proposed as a fast and efficient EMVS accelerator by realizing the most critical and time-consuming stages including event back-projection and volumetric ray-counting on FPGA. [related project]