Image credit: Unsplash

Image credit: Unsplash

Abstract

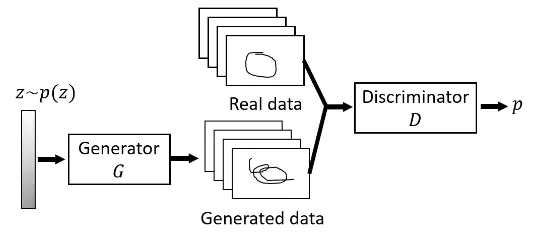

The relentless efforts towards power reduction of integrated circuits have led to the prevalence of near-threshold computing paradigms. With the significantly reduced noise margin, therefore, it is no longer possible to fully assure power integrity at design time. As a result, designers seek to contain noise violations, commonly known as voltage emergencies, through various runtime techniques. All these techniques require accurate capture of voltage emergencies through noise sensors. Although existing approaches have explored the optimal placement of noise sensors, they all exploited the statistical modeling of noise, which requires a large number of samples in a high-dimensional space. For large scale power grids, these techniques may not work due to the very long simulation time required to get the samples. In this paper, we explore a novel approach based on generative adversarial network (GAN), which only requires a small number of samples to train. Experimental results show that compared with a simple heuristic which takes in the same number of samples, our approach can reduce the miss rate of voltage emergency detection by up to 65.3% on an industrial design.